?1、熱插拔概述 熱插拔(hot-plugging或Hot Swap)即帶電插拔,熱插拔功能就是允許用戶在不關閉系統,不切斷電源的情況下取出和更換損壞的硬盤、電源或板卡等部件,從而提高了系統對災難的及時恢復能力、擴展性和靈活性等,例如一些面向高端應用的磁盤鏡像系統都可以提供磁盤的熱插拔功能。 一方面,在軍事、電信、金融等領域,設備投入運行后,必須夜以繼日地運轉,對這些設備的部件進行拆裝維修、維護、擴展時,系統不能停機,停機則意味著重大的經濟損失。這就要求設備部件能夠在系統帶電運行的情況下進行接入或者移出。 另一方面,對連接到總線上的設備,對單個設備進行插入或者拔出的時候,不能對總線產生較大干擾,否則會在總線上產生較大的噪聲,引起總線上其他設備的停機或者誤碼產生,影響整條總線業務。熱插拔技術正是在這種需求下應運而生。 民用熱插拔技術開始于PC機的開發中,從586時代開始,系統總線都增加了外部總線的擴展,此時的系統總線已經初步滿足熱插拔的要求。1997年開始,新的BIOS中增加了即插即用功能的支持,雖然這種即插即用的支持并不代表完全的熱插拔支持,僅支持熱添加和熱替換。1、在系統開機情況下將損壞的模塊移除,還可以在開機情況下做更新或擴容而不影響系統操作。2、由于熱插拔零件的可靠度提升,還可以將它們用做斷電器,而且因為熱插拔能夠自動恢復,有很多熱插拔芯片為系統提供線路供電情況的信號,以便系統做故障分析,因此減少了成本。早期的熱插拔技術實現路徑主要是是靠電容和電感,實現對沖擊的瞬間抑制,但是這種做法有可能導致電源受到巨大沖擊,然后系統有可能因此發生復位和重啟,后來依靠三極管技術和分立器技術,用新型的熱插拔芯片,逐漸實現了熱插拔技術電流控制目標。 按照電路帶電插拔時對器件和信號的影響程度,把帶電插拔的防護設計分為四個等級。介紹如下。但該四個等級是根據普通邏輯器件(如驅動器等)的電路結構來定義的,FPGA、CPLD等大邏輯器件的端口結構與普通邏輯器件有較大的區別,結構更加復雜,但仍可以等效為普通邏輯器件的熱插拔等級。 具有0級防護設計的電路板應在先關斷主電源的情況下才能安全的帶電插拔。它沒有對瞬變電流或突變電壓的抑制保護,插拔過程中插入電路板接口也不能進入高阻狀態。如果插入電路板在系統沒有斷電情況下就進行帶電插拔,板上的接口器件或其他元件很可能受到損壞。只能達到0級防護設計的電路板不能帶電插拔。 2)1級防護(Partial Power Down) 具有1級防護設計的電路板在斷電時能限制帶電總線和插入電路板接口之間的電流,從而防止插入電路板受到損壞。這種瞬態電流限制就能保證在不打斷主電源情況下帶電插拔電路板,但是在帶電插拔期間,主系統必須暫停信號傳輸。這種防護設計需要使用IOFF電路。 具有2級防護設計的電路板具有帶電插拔性能,它能防止插入電路板插拔時的驅動沖突。2級防護設計除了具有1級防護設計的能力外,信號端還能在電源電壓上升到指定值之前保持高阻狀態,在電源電壓超過這個指定值后會按照設置狀態輸出。電路板斷電時,在電源電壓下降到預定電壓值之前輸出保持為驅動邏輯電平,然后變成高阻狀態。按照2級防護設計的要求,電路板帶電插拔期間總線上的數據傳輸可能會被打斷。2級防護設計既需要1級防護設計中的IOFF電路,也需要上電3態電路(PU3S)。 具有3級防護設計的電路板在帶電插拔時對系統電源和信號沒有其他的限制、約束和要求。帶電插拔和數據交換可同步進行,即在任何情況下進行插、拔操作都不會破壞數據,當然更不會損壞器件。為了達到這些要求,3級防護設計同時需要IOFF、PU3S和預充電I/O。

在以前,我們使用電腦或者其他電子設備時,總會受到警告:不能帶電插拔,如果我們帶電插拔,輕則造成系統死機或者重啟,重則造成接口電路硬件損壞,造成巨大損失。這是什么原因呢,對不支持熱插拔的系統,帶電插拔為什么會造成如此嚴重的后果? (1) 熱插拔引發閂鎖效應:熱插拔前設備之間可能存在較高電位差,如果不采取相應措施這種電位差將對設備上的IC 芯片構成嚴重危害,尤其是CMOS器件,有可能引發閂鎖效應。 (2)熱插拔誘發靜電問題:雖然冷插拔過程中也有靜電問題,但是由于熱插拔時一部分電路是處于上電工作狀態,因此熱插拔時的靜電干擾會引發諸如“閂鎖效應”之類惡性故障,除此之外,熱插拔對于穩定工作的背板設備的靜電干擾使得本來在設備內部的背板連接器變成了被靜電直接擊中的外部接口。 (3)熱插拔導致浪涌問題:當單板插入機框時,機框中其他設備已處于穩定工作狀態,所有儲能電容均被充滿電,而單板上的電容沒有電荷,當設備與主板接觸時設備上的電容充電將在短時間內從電源系統吸入大量電能,在供電線路上形成一股比正常工作電流高出數倍的浪涌電流。浪涌電流會使電源出現瞬時跌落導致系統復位、引發閂鎖效應、導致連接器電路板金屬連線和電路元件燒壞。 (4)熱插拔對總線造成干擾:總線上插入板卡時,由于新插入板卡電容的充電以及上電過程中一些低阻抗通道的存在,會產生極大的浪涌電流,拉低總線電平,對總線上其他設備產生干擾,影響總線上其他設備的正常運行。同時插拔時也對總線接口帶來靜電問題。(1) 定義:閂鎖(Latch up)是指CMOS器件所固有的寄生雙極晶體管被觸發導通,在電源和地之間形成一個低阻通路。(2)故障現象:CMOS芯片的電源和地之間大電流通過,導致芯片自身燒毀失效,嚴重時會波及周圍的電路和易燃器件(如:鉭電容)。

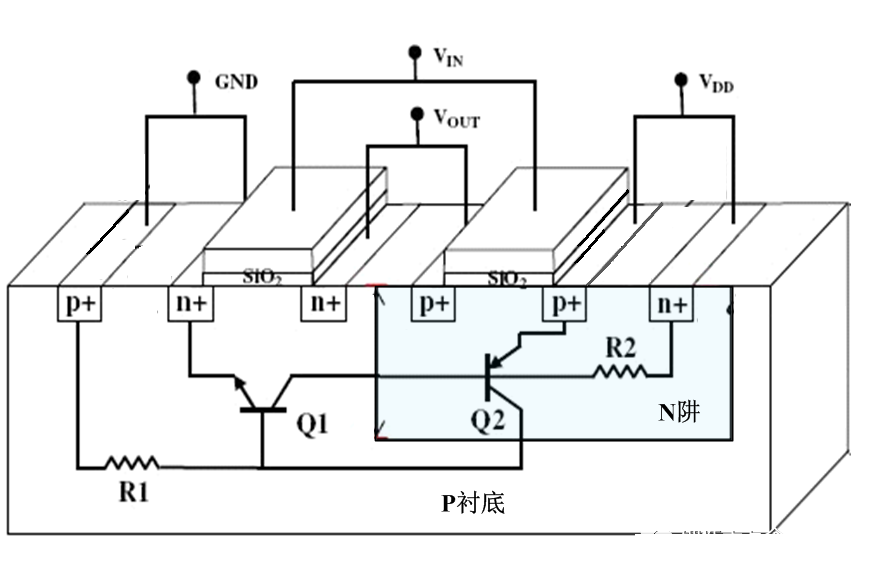

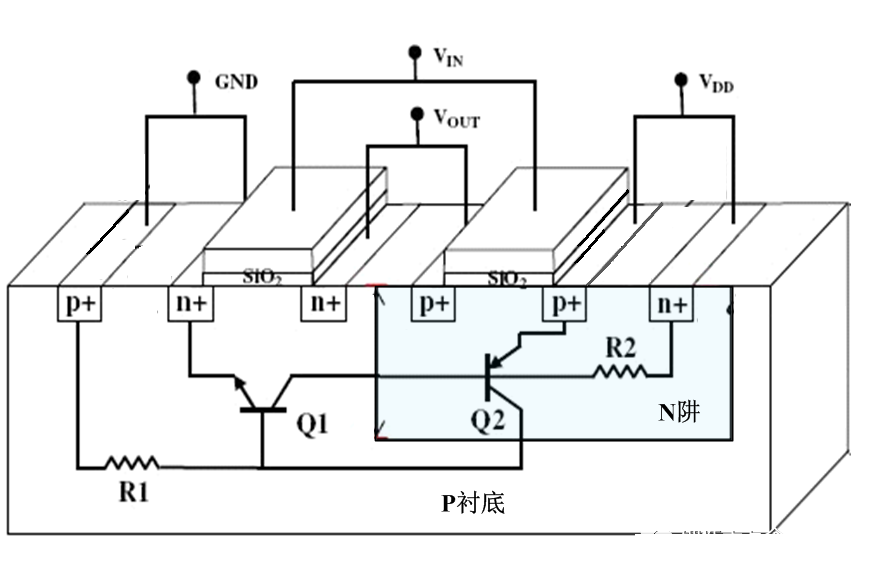

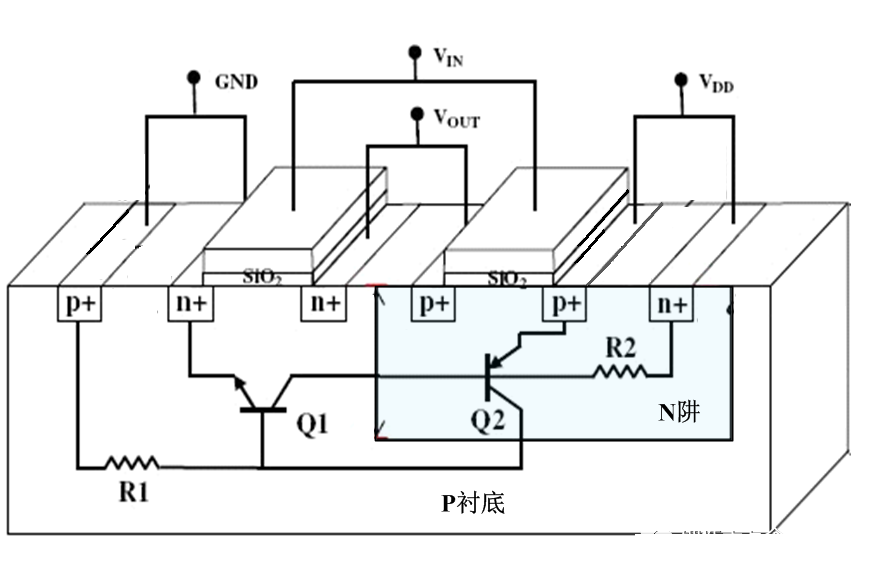

如圖2-1所示,CMOS發生閂鎖效應時,其中的NMOS的有源區、P襯底、N阱、PMOS的有源區構成一個n-p-n-p的結構,即寄生晶體管(Q1、Q2),本質是寄生的兩個雙極晶體管的連接。P襯是NPN的基極,也是PNP的集電極,也就是NPN的基極和PNP的集電極是連著的;N阱既是PNP的基極,也是NPN的集電極。再因為P襯底和N阱帶有一定的電阻,分別用R1和R2來表示。當N阱或者襯底上的電流足夠大,使得R1或R2上的壓降為0.7V,就會是Q1或者Q2開啟。例如Q1開啟,它會提供足夠大的電流給R2,使得R2上的壓降也達到0.7V,這樣R2也會開啟,同時,又反饋電流提供給Q1,形成惡性循環,最后導致大部分的電流從VDD直接通過寄生晶體管到GND,而不是通過MOSFET的溝道,這樣柵壓就不能控制電流。 元器件中的寄生晶體管連接關系可以用集總元件來表示,如圖2-2所示,其結構實際上是一個雙端PNPN結結構,如果再加上控制柵極,就組成門極觸發的閘流管。該結構具有如圖3所示的負阻特性,該現象就稱為閂鎖效應(閂鎖本是閘流管的專有名詞)。即雙端PNPN結在正向偏置條件下,器件開始處于正向阻斷狀態,當電壓達到轉折電壓時,器件會經過負阻區由阻斷狀態進入導通狀態.這種狀態的轉換,可以由電壓觸發(=0),也可以由門極電流觸發(≠O)。門極觸發大大降低了正向轉折電壓。

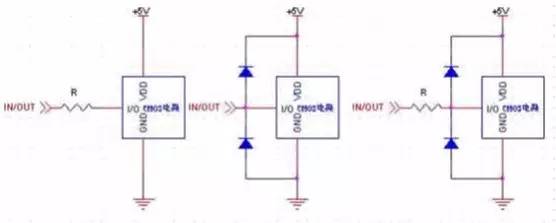

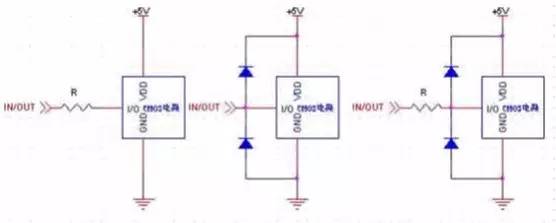

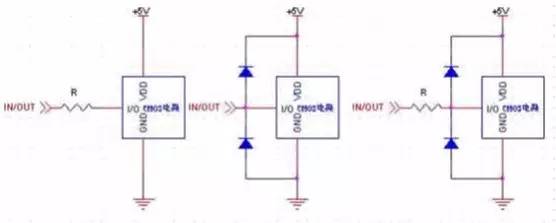

兩個寄生晶體管工作時,形成正反饋電路,加深可控硅導通,造成的結果在器件級的描述一樣,一股大的電流將由電源流向接地端,導致一般正常電路工作中斷,甚至會由于高電流散熱的問題而燒毀芯片(1)存在正反饋:寄生雙極極晶體管回路電流增益必須大于1。β1β2.>1(2)外觸發條件:一個維持足夠長時間的外部電流,使雙極型晶體管導通起來。(3)電流供應能力:外電路能持續提供維持閂鎖所必須的電流。(1)輸入/輸出腳電壓:高電平比芯片電源還高,低電平比芯片地還低,這是最常見的誘發原因。(1)通訊管腳先于電源管腳接通導致CMOS器件的輸入/輸出腳電壓高于電源電壓或低于地電壓。(2)板卡插入瞬間由于電容充電電流,導致背板電源異常波動,引發器件閂鎖。(4)板卡拔出瞬間由于電感的感生電壓導致背板CMOS器件閂鎖。(1) 電路接口部分采用防護措施:防止觸發信號的引入。(2)COMS器件輸入/輸出端加限流電阻。驅動長線負載時,做好匹配,以減小過沖、下沖,允許的條件下,可在CMOS器件端口處加兩個二極管,一個接地,一個接電源。系統具有用戶可操作的I/O,在I/O串接一個電阻限流,并可在端口處加兩個二極管,一個接地,一個接電源。

(3)小功耗器件電源線上串限流電阻,電源串電阻,限流,消除閂鎖導致器件的損壞。(6)帶電插拔時,要求連接順序為:GND、低電壓電源、高電壓電源、I/O。其中電壓以絕對值計。相同幅值的正負電源同時上電,可使兩者的影響相互抵消。(7)做好電源去耦,避免上電時或工作中,電源電壓上沖或下沖導致的閂鎖。

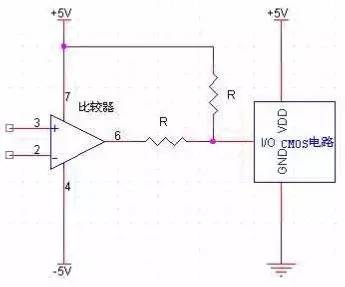

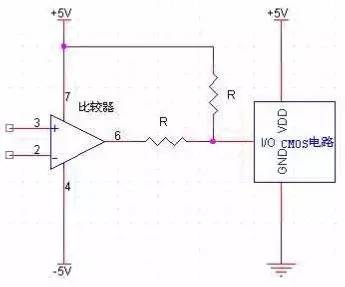

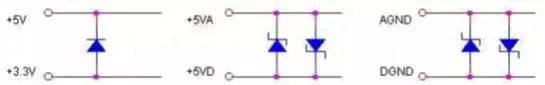

(8)數字電路與模擬電路相接時,如下圖,通過電阻分壓比用二極管箝位效果要好。

(9)繼電器等感性負載,加反接二極管吸收浪涌電流。

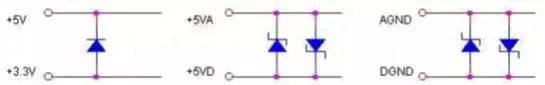

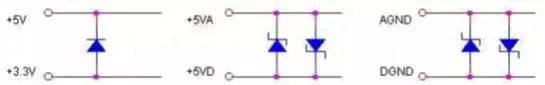

(11)高低電壓電源之間接二極管,避免在上下電時,低電壓電源端電壓超過高電壓電源端過多,起箝位作用。(12)同電壓的不同電源之間加兩個相互反接的肖特基二極管。

(13)AGND與DGND之間加兩個相互反接的肖特基二極管。1、《工程技術基礎-熱插拔知識詳解及案例分析教材》百度文庫,作者不詳3、KyechongKim a, Agis A. Iliadis ,Latch-upeffects in CMOS inverters due to high power pulsed electromagnetic interference4、 GENDA.HU,ABetter Understand of CMOS Latch-Up